一、实验目的:

1.掌握“Quartus II 4.0”中程序的编写、编译以及仿真的方法。

2.掌握FPGA程序下载的方法。

3.掌握pn序列产生及相应编译码的基本方法。

二、实验内容:

1.在“Quartus II 4.0”中编写产生pn序列的程序。然后,编译和仿真。

2.将程序下载到FPGA中,然后进行验证。

三、实验仪器:

1.光纤通信实验系统1台。

2.JTAG下载线1根。

3.电脑1台。

4.示波器1台。

四、实验原理:(以PN序列为例)

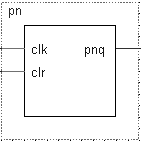

程序输入输出口定义:

输入口:clk pn序列时钟输入。

clr 上电复位端。

输出口:pnq pn序列输出口。

pn序列模块图形如图1所示。

图1 pn序列模块图

程序设计要求:

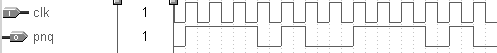

1.pn序列输出信号要与其时钟上跳沿对齐。参考波形如图2所示:

图2 pn序列输出信号波形图

2.产生7位8Kbit/s的pn序列。

3.记录下pn序列的波形。

程序设计提示:

1.clr端是用来初始化程序内部寄存器的状态的,在上电的瞬间,在这个端口会出现一个下跳沿。此后,该端口一直保持低电平的状态。其波形如图3所示:

![]()

图3 clr端口波形图

clr端在电端和光端FPGA都有专门的定义的引脚,可以参见附录一。

五、实验注意事项:

1.在连接JTAG下载线时,JTAG下载线有红色的一边靠左,然后插入实验系统的程序下载断口。

2.程序下载到FPGA中可以马上使用,不能断电,断电后下载的程序会丢失。

六、实验步骤:

1.在电脑上运行“Quartus II 4.0”。

2.用VHDL语言或者用画图的方式编写产生pn序列的程序。

3.编译程序并进行仿真。然后,分配好管脚。

4.关闭实验系统电源。然后,用JTAG下载线连接电脑的并口和实验系统的程序下载口J601。

5.打开系统电源。将程序下载到FPGA中,然后用示波器观察相应的测试点。

七、实验报告:

1.描述pn序列产生及编译码的方法。

2.记录相关测试点的波形并与仿真结果相比较。

3.用VHDL语言编写一程序产生相应的结果。

0769-81105095

158-9969-7899