光纤传输综合实验

综合性实验

一、实验目的

1、掌握CMI编译码的方法。

2、掌握波分复用技术及实现方法。

3、掌握变速率/解变速率时分复用的实现方法。

4、掌握变速率/解变速率波分复用的实现方法。

5、掌握时分复用技术和波分复用技术的灵活搭配使用。

二、实验内容

1、CMI码的光纤传输。

2、了解波分复用原理及实现方法。

3、了解变速率时分复用的原理及实现方法。

4、实现四台计算机和语音同时通信

三、实验仪器

1.光纤通信实验系统1台。

2.示波器1台。

3.光纤跳线1根。

2.波分复用器2个。

4.光纤活动连接器1个。

5.计算机若干台串口通信电缆若干根(数量根据计算机数量配置)

四、实验原理

1.线路码型

数字光纤通信与数字电缆通信一样,在其传输信道中,通常不直接传送终端机(例如PCM终端机)输出的数字信号,而需要经过码型变换,使之变换成为适合于传输信道传输的码型, 称之为线路码型. 在数字电缆通信中, 电缆中传输的线路码型通常为三电平的“三阶高密度双极性码”, 即HDB3码,它是一种传号以正负极性交替发送的码型。在数字光纤通信中由于光源不可能发射负的光脉冲,因而不能采用HDB3码,只能采用“0”“1”二电平码。但简单的二电平码的直流基线会随着信息流中“0”“1”的不同的组合情况而随机起伏,而直流基线的起伏对接收端判决不利,因此需要进行线路编码以适应光纤线路传输的要求。

线路编码还有另外两个作用:

其一是消除随机数字码流中的长连“0”和长连“1”码,以便于接收端时钟的提取。

其二是按一定规则进行编码后,也便于在运行中进行误码监测,以及在中继器上进行误码遥测。

2.CMI码

CMI(Coded Mark Inversion)码是典型的字母型平衡码之一。CMI在ITU-T G.703建议中被规定为139 264 kbit/s(PDH的四次群)和155 520 kbit/s(SDH的STM-1)的物理/电气接口的码型。其变换规则如下表所示:

|

输入码字 |

CMI码 |

|

模式1 |

模式2 |

|

0 |

01 |

01 |

|

1 |

00 |

11 |

CMI由于结构均匀,传输性能好,可以用游动数字和的方法监测误码,因此误码监测性能好。由于它是一种电接口码型,因此有不少139 264 kbit/s的光纤数字传输系统采用CMI码作为光线路码型。除了上述优点外,它不需要重新变换,就可以直接用四次群复接设备送来的CMI码的电信号去调制光源器件,在接收端把再生还原的CMI码的电信号直接送给四次群复用设备,而无须电接口和线路码型变换/反变换电路。其缺点是码速提高太大,并且传送辅助信息的性能较差。

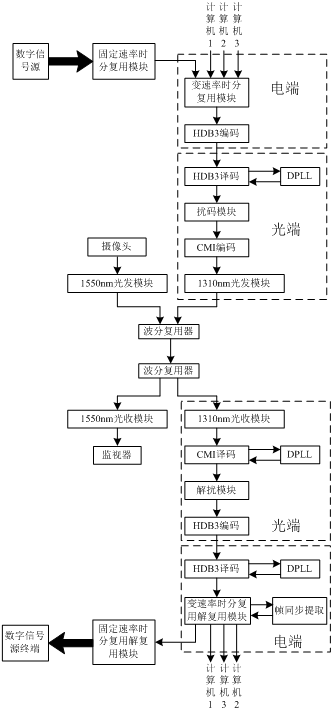

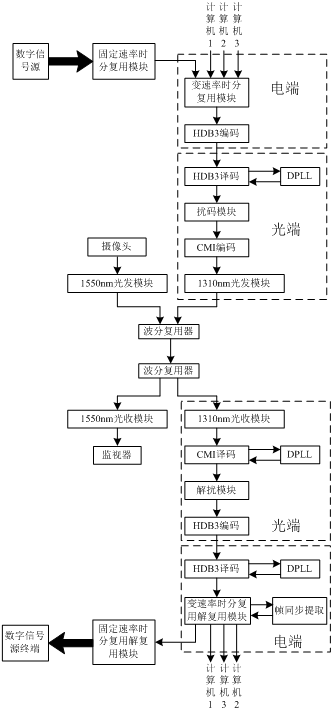

1. CMI编码原理框图

图1 CMI编码原理框图

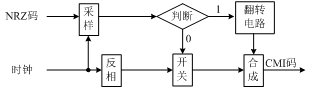

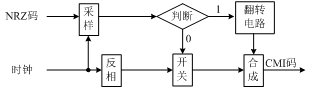

2. CMI译码原理框图

图2 CMI译码原理框图

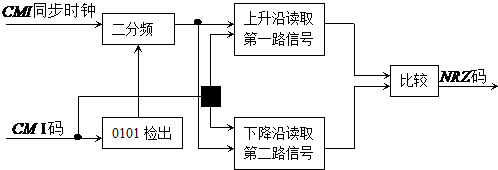

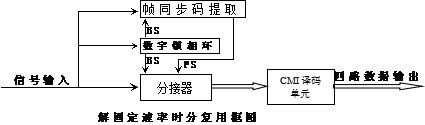

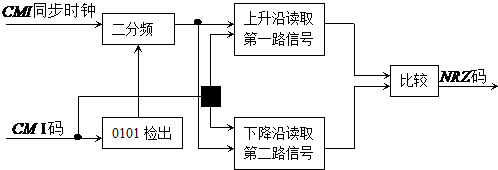

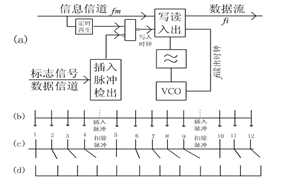

4、 变速率时分复用原理

图3 变速率时分复用原理图

各组成模块的功能说明如下:

码速调整: 将输入信号用128kbit/s的时钟进行CMI编码。使输入信号具有 同码速。输出信号的速率为256kbit/s。

复接器: 将4个支路已经同步的信码流和四位巴克码复接成一个高速率的信号。输出信号的速率为2048kbit/s。

时钟源: 为整个复接电路提供稳定的时钟信号。

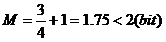

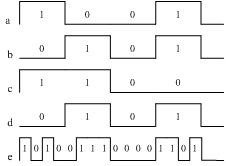

逐比特复接也叫逐位复接。逐位复接的示意图如下图所示。(a)、(b)、(c)、(d)是4个被复接支路的信号(基群数字信号),(e)是复接后的数字信号。复接过程是这样的:首先取基群的位码,接着取第二基群的位码,再取第三基群的位码,再取第四基群的位码,轮流将4个支路的位码取值一次后再进行第二位码取值,方法仍然是:首先取基群的第二位码,接着取第二基群的第二位码,再取第三基群的第二位码,轮流将4个支路的第二位码取值一次后再进行第三位码取值,依此类推,一直循环下去。这样得到的图中(e)序列就是复接后的二次群序列。可以看出,复接后每位码的宽度只是原来支路每位码宽度的1/4,换言之,容量增加了4倍。复接时,缓冲存储器是不可少的,其原因可由图4-1看出:当复接器在复接第二、第三和第四基群的位码时,基群的第二位码,第三位码……不断送来,而这些码位要等第四基群的位码复接完了才能复接它们。因此,每个基群都需要存储器先把它们存储起来。由于是按位复接,循环周期不长,存储器所需的容量不大,制作比较简单。缓冲存储器的容量由下式决定:

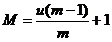

式中u为复接单位的比特数。上图中每次复接一位,即u=1;m为被复接的基群数,这里m=4。这样二次群复接器所需的容量M为:

式中的1bit是先写进去以便读出的存储起始撞,3/4是读第二、三、四基群的位码时所需存储容量。可见,缓冲存储器的容量取2bit就够了。

图4 缓冲存储器波形图

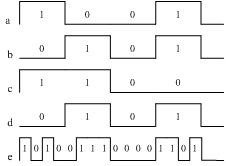

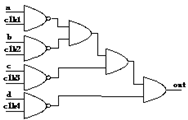

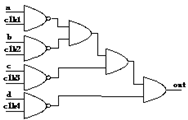

按位复接简易原理框图:

图5 按位复接原理框图

变速率时分复用和固定速率时分复用主要区别在于变速率时分复用采用了按位复接的方式而固定速率时分复用采用的是按码字复接。按位复接设备简单,但是信号的完整性比较差。按码字复接信号完整性好,但设备较复杂,所需缓冲存储器的容量较大,目前应用的很少。

码速调整有三种方式:正码速调整;正/负码速调整;正/零/负码速调整。

ITU—T推荐使用正码速调整和正/零/负码速调整方式。我国大部分复用设备采用正码速调整方式,也有采用正/零/负码速调整方式的。

目前应用的多是“脉冲插入同步”方式,这种方式是利用插入脉冲的方法来实现调整的。

所谓正码速调整就是将被复接的低次群的码速都提高,使其同步到某一规定的较高的码速上。例如在PCM基群的数码率标称值都是2 048kb/s,但由于各个独立的时钟源总是存在偏差,因此,可根据复接帧的要求,确定脉冲的插入数目,使每个基群的数码率均由2 048kb/s填充到所要求的数码率,二次群复接时为2112kb/s。这样,码速都提高了,又达到了相互同步的目的。由于是用提高码速来使其同步,故称为正码速调整。

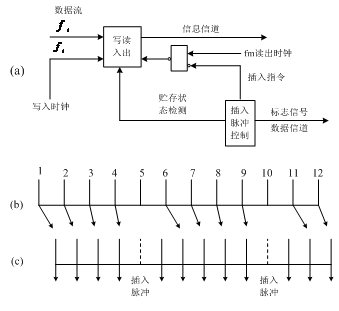

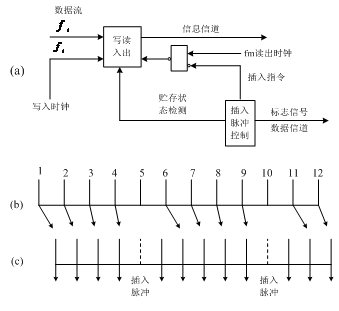

在系统中,首先对输入的四路信号按一定速率进行编码,以便使四路信号速率的标称值相同,编码方式可以采用多种方式(如CMI、DMI,5B6B,4B1H等等),然后再对编码后的信号进行脉冲插入同步的正码速调整,下面,我们对正码速调整中插入脉冲部分的原理作简单介绍。采用脉冲插入同步的正码速调整的原理如图6所示。该图只绘出一个支路的码速调整插入部分情况,去插入部分和复接部分没有绘出。

图6 脉冲插入同步方式插入部分的原理示意图

(a) 方框图;(b)支路输入数码流fi,(c)码速调整后的数码流fm;

基群输入的数字信号先写入到一个缓冲存储器,写入速率是编码速率,读出时钟频率则是码速调整后的速率fm,而fm>fi,所以存储器是读得快写得慢,即存储器处于“快读慢写”状态。快读慢写会出现什么结果呢?从图(b)和(c)可以看出,第1个脉冲经过一段时间后读出,第2个脉冲的读出,其经过的时间长度比前者要短一些,因读出速度比写入速度快,以后的写入与读出时间差,即相位差愈来愈小,在第6个脉冲时两者相位差已很小,即将出现取空状态,当相位差小到一定程度时,由相位比较器(在缓冲存储器中)发出插入请求,要求插入脉冲控制电路发出一个插入指令,停止一次读出,同时在此瞬间插入一个脉冲,如图中虚线位置所示。

插入脉冲是不携带信息的,所以在接收端应把它去掉,为此,发送端在插入脉冲的同时,必须发出一个标志信号通知接收端,据此判别出哪些是插入脉冲,然后把它去掉以恢复原始信号。

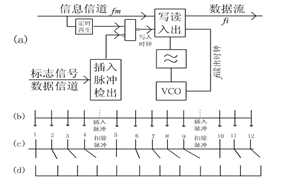

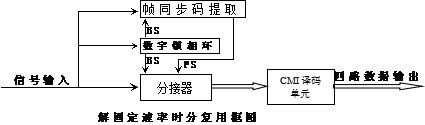

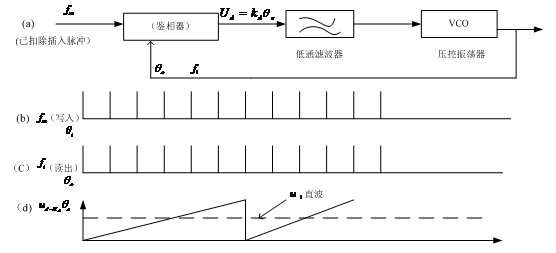

6、变速率时分解复用原理

分接端的原理如图7所示。

图7 分接端原理框图

各组成模块的功能说明如下:

分接器: 把输入信号分接成4咱,分路送入缓冲存储器。

数字锁相环: 从输入信号中提取定时信息,为其他模块提供时钟。

帧同步码提取:为分接器提供帧同步信号

去插入原理示意图如图8所示。

图8 同步脉冲去插入原理示意图

(a)方框图;(b)码速调整后的数码流fm;

(c)扣除插入脉冲后的接收信号;(d)恢复后的原数码流fi

在接收端,当收到发送端的标志信号后,它连同信号一起通过一个标志信号检出电路而被检出,因而产生一个“消插指令”,把写入脉冲禁掉一个,也就是不使插入脉冲写入存储器。如图(c)所示,即原虚线所示的位置空着了。

这时,数码与原来的数码次序一样(因已扣除了插入脉冲),但时间间隔是不均匀的,中间有间隙。因此,在接收端,要恢复原数码,必须从图(c)波形中,提取时钟fi,即是将已去掉插入脉冲的数码流均匀化。这一任务用一个锁相环来完成。

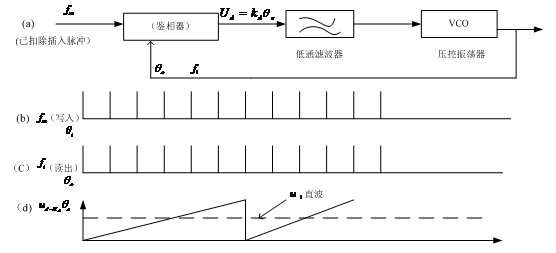

锁相环框图如图9所示。由鉴相器、压控振荡器和低通滤波器组成。压控振荡器的输出是读出时钟fi,相位为θ0。鉴相器有两个输入信号:一个是写入时钟fm,它是已扣除插入脉冲的序列,其相位为θi;另一个是压控振荡器的输出fi。鉴相器将两信号进行相位比较,鉴相器的输出电压ud与它们的相差θe成比例,经过低通滤波器滤出的直流成分uc,即为其平均值。uc作为VCO的控制电压,通过环路的作用,使fi与fm同步,即振荡器振荡在平均频率fi上,使读出脉冲的间隔均匀了。

图9 收端读出脉冲均匀化

(a) fm(已扣除塞入脉冲);(b) fm(写入);(c) fi(读出);(d) ud=kdθe

为了使塞入脉冲的塞入和去塞入更可靠一些,往往采用定位塞入法。而塞入脉冲的标志信号往往是与帧同步信号一起传送,这时数据信道与信息信道合成为一个信道。

综上所述,接收端工作过程要点如下:

1、 定时再生电路再生fm,作为写入时钟。

2、 由插入脉冲检测电路检测出插入脉冲后,发出扣除插入脉冲指令,把写入脉冲禁掉一个,即不使插入脉冲写入存储器。

3、 将已扣除塞入脉冲的fm送到锁相环鉴相器,通过锁相环的作用,获得读出时钟fi,即恢复为原来支路的频率fi。

4、 由于锁相环的存在,不可避免要产生抖动。

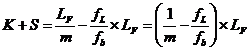

下面讨论正码速调整的基本参数

设 fb为标称复接比特率;

fL为标称支路比特率;

m为支路数;

K为每帧中对应每个支路的非信息比特数;

G为每帧中对应每个支路的信息比特数。

则有:

(1)、帧长LF

帧长表示每帧中信息比特与非信息比特的总和为

LF=m(G+K) (式5-1)

(2)、帧频fF

帧频fF表示每单位时间内的帧数,

(式5-2)

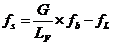

(3)、标称码速调整速率fs(fi)

标称码速调整速率fs也称为标称插入速率,是当支路速率与复接速率都等于标称值时,插入的调整比特的速率。

(式5-3)

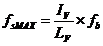

(4)、每支路码速调整频率fsMAX。

或

(式5-4)

式中IV是每帧每支路可用于码速调整的比特数。

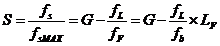

(5)、标称码速调整比S

S是标称码速调整速率与每支路调整速率之比:

(式5-5)

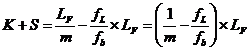

(6)、正码速调整的基本关系式

由(式5-1)得:

(式5-6)

由(式5-5)得:

(式5-7)

将式(3.7)代入式(3.6)可得:

(式5-8)

式(5.8)就是正码速调整的基本关系式,其中,支路比特速率fL、复接比特率fb和支路数m都是已知量。帧长LF对应每个支路的非信息比特数K及标称码速调整比S是基本设计量。在这三个设计量中通常取帧长LF做自变量。每取一个LF值即可按基本公式求得左端的数值,该数值的整数部分就是K值,小数部分就是S值。

五、实验步骤

A.CMI编译码步骤

1.关闭系统电源。

2.按实验十七的实验步骤将1310nm光收发模块调为最传达输状态。然后,关闭系统电源,保留光纤跳线的连接,拆除其它连线。

3.将光端FPGA的J700设置为“外部”。

4.按如下方式连接:

光端FPGA模块

(PN序列一) |

P720--P716 |

光端FPGA模块

(CMI编码模块信号输入) |

光端FPGA模块

(PN序列一时钟) |

P719--P714 |

光端FPGA模块

(CMI编码模块时钟输入) |

光端FPGA模块

(CMI编码输出) |

P715--P100 |

1310nm光发模块

(数字光发信号输入) |

1310nm光收模块

(光收模块数字输出) |

P106--P724 |

光端FPGA模块

(CMI译码信号输入) |

5.打开系统电源,用示波器观测光端FPGA的TP720和TP715,比较PN序列编码前后的波形有何变化。再用示波器观测TP720和TP723的波形,比较编码前和译码后的波形。

B.变速率时分复用

数字信号源模块

(数字信号源一) |

P300—P741

————→ |

固定速率时分复用模块

(复用输入信号一) |

数字信号源模块

(数字信号源二 ) |

P301—P740

————→ |

固定速率时分复用模块

(复用输入信号二) |

数字信号源模块

(数字信号源三) |

P302—P739

————→ |

固定速率时分复用模块

(复用输入信号三) |

数字信号源模块

(数字信号源四) |

P303—P738

————→ |

固定速率时分复用模块

(复用输入信号四) |

固定速率时分复用模块

(复用输出) |

P742—P603

————→ |

电端FPGA

(变速率时分复用输入信号一) |

光端FPGA

(PN序列一信号输出) |

P720—P602

————→ |

电端FPGA

(变速率时分复用输入信号二) |

1.打开系统电源。用示波器分别观测TP603和TP608、TP602和TP607、TP601和TP606、TP600和TP605分别为CMI编码前后的波形。

2.用示波器观测TP614,观测复用后的波形。

C. 变速率时分解复用

数字信号源模块

(输出一) |

P300—P741 |

固定速率时分复用模块

(复用输入一) |

数字信号源模块

(输出二 ) |

P301—P740 |

固定速率时分复用模块

(复用输入二) |

数字信号源模块

(输出三) |

P302—P739 |

固定速率时分复用模块

(复用输入三) |

数字信号源模块

(输出四) |

P303—P738 |

固定速率时分复用模块

(复用输入四) |

固定速率时分复用模块

(复用输出) |

P742—P603 |

电端FPGA

(变速率时分复用输入一) |

光端FPGA

(PN序列一信号输出) |

P720—P602 |

电端FPGA

(变速率时分复用输入二) |

电端FPGA

(变速率时分复用复用输出) |

P614—P618 |

电端FPGA

(HDB3编码信号输入) |

电端FPGA

(HDB3编码信号输出一) |

P617—P800 |

2M接口一

(电平变换信号输入一) |

电端FPGA

(HDB3编码信号输出二) |

P616—P802 |

2M接口一

(电平变换信号输入二) |

2M接口一

(电平变换信号输出) |

P801—P803 |

2M接口一

(电平反变换信号输入) |

2M接口一

(电平反变换信号输出一) |

P805—P622 |

电端FPGA

(HDB3译码信号输入一) |

2M接口一

(电平反变换信号输出二) |

P804—P621 |

电端FPGA

(HDB3译码信号输入二) |

2M接口一

(电平反变换信号输出一) |

P805—P624 |

电端FPGA

(数字锁相环信号输入) |

电端FPGA

(HDB3译码信号输出) |

P620—P626 |

电端FPGA

(帧同步提取信号输入) |

电端FPGA

(HDB3译码信号输出) |

P620—P632 |

电端FPGA

(变速率时分复用解复用输入) |

电端FPGA

(变速率时分复用解复用输出一) |

P636—P745 |

数字信号终端

(固定速率时分复用解复用输入) |

电端FPGA

(速率时分复用解复用输出一) |

P636—P744 |

数字信号终端

(数字锁相环信号输入) |

1.打开系统电源。用示波器观察电端FPGA模块测试点TP635和光端FPGA模块测试点TP720的波形。比较PN序列一在变速率时分复用前和解复用后的波形。

2.将数字信号源其中的一路拨为帧同步码(“01110010”),比较数字信号源模块和数字信号源终端模块的发光二极管的显示。

D.波分复用

1.有三种连线方式分别代表了模拟信号和模拟信号一起传输、模拟信号和数字信号混传、数字信号和数字信号一起传输,选择其中一种:

|

方式一 |

模拟信号源模块

(正弦波输出) |

P410—P104

————→ |

1310nm光发模块

(模拟光发输入) |

模拟信号源模块

(三角波输出) |

P401—P204

————→ |

1550nm光发模块

(模拟光发输入) |

|

方式二 |

模拟信号源模块

(正弦波输出) |

P410—P104

————→ |

1310nm光发模块

(模拟光发输入) |

光端FPGA

(PN序列一) |

P720—P200

————→ |

1550nm光发模块

(数字光发输入) |

|

方式三 |

光端FPGA

(PN序列一) |

P720—P100

————→ |

1310nm光发模块

(数字光发输入) |

光端FPGA

(PN序列二) |

P718—P200

————→ |

1550nm光发模块

(数字光发输入) |

2.在上表中的三种连线方式任选其一连接好波分复用器。

3.如果传输的使模拟信号,则按实验十四来进行实验。如果传输的是数字信号则按实验十七来进行实验。

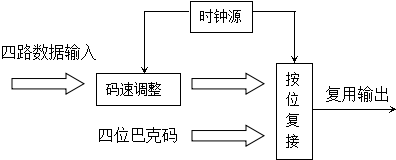

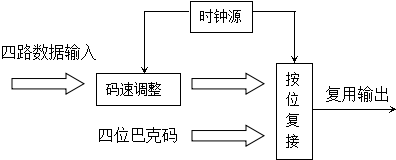

E. 时分复用技术和波分复用技术组合

图10 实验框图

1.实验框图如图10所示,参考前面的实验自己设计连线方式并连接好。

2.打开系统电源。调节光收发模块的状态,使计算机数据能够正常传输,图象能够正常传输。

六、实验报告

1.简述CMI编译码的原理。

2.记录各测试点的波形。

(式5-8)

(式5-8)